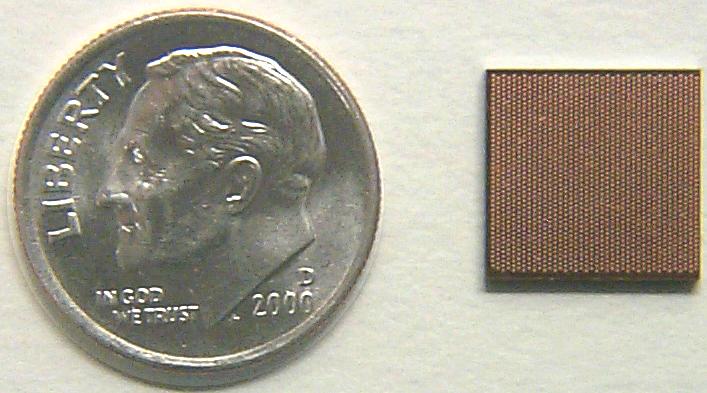

Intel zeigte gestern erstmals einen mit 0.09µm-Technologie hergestellten SRAM-Speicherchip. SRAM ist im Vergleich mit DRAM weitaus schneller und wird daher vor allem als Cachespeicher für Prozessoren benutzt. Die hohe Performance erkauft man sich aber mit enormen Produktionskosten. Um ein Bit speichern zu können, benötigt SRAM sechs Transistoren, DRAM nur zwei. Beim Pentium III Coppermine belegt der lediglich 256KB große Cache etwa ein Drittel (30mm²) der gesamten Chipfläche.

Mit der neuen 0.09µm Prozesstechnik kann man den Platzbedarf einer Zelle von 2µm² auf 1µm² senken. So bekommt Intel auf nur 109mm² Chipfläche die 6.5MB Cache unter. So große Caches wird es natürlich vorerst nur in Intels teuren Serverprozessoren der Itanium-Reihe geben. Dort ist im nächsten Jahr der 64Bit Madison mit 6MB L3-Cache geplant – allerdings noch mit 0.13µm-Technologie. Die 3MB L3-Cache des Madison-Vorgängers McKinley, den es im Herbst geben soll, benötigen mit alter 0.18µm-Technologie 175mm² Platz.

Doch auch im Desktop-Bereich wird die 0.09µ-Technologie Vorteile mit sich bringen. Zwar werden 6MB Cache so schnell nicht im Heimbereich Einzug halten, Intel bleibt aber genügend Platz, um dem nächsten Pentium 4 Prozessor Prescott z.B. einen größeren L1-Cache zu spendieren. Bis zur Serienreife der 0.09µm Prozesstechnik im Herbst 2003 hat Intel ja noch etwas Zeit für Designänderungen am Prozessorkern.

Quelle: Pressemitteilung

Neueste Kommentare

19. April 2024

17. April 2024

17. April 2024

5. April 2024

23. März 2024

22. März 2024